Registre TMR0 (Timer 0)

Il s’agit d’un registre spécial situé à l’adresse 0x01 (banque 0) de la mémoire des données (Data RAM).

Ce registre contient un nombre de 8 bits (0 à 255 en numération décimale).

Le module TMR0 (Timer 0) possède deux modes de fonctionnement :

• Le mode timer

• Le mode compteur

1- Le mode timer

Pour configurer le module TMR0 en mode timer, il faut au préalable que :

T0CS = 0 (bit 5 du registre OPTION_REG)

Le contenu du registre TMR0 est alors incrémenté à chaque cycle de l’horloge interne.

1 cycle correspond à une durée de 1 µs pour un oscillateur à quartz de 4 MHz (1 cycle = 4 / FOSC).

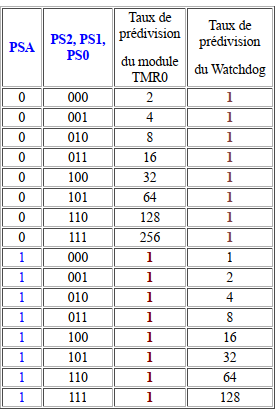

En toute rigueur, cela est vrai si le taux de prédivision (prescaler) est réglé à 1 (bit 3 du registre OPTION_REG = PSA = 1).

Avec un taux de prédivision de 128 (PSA = 0, PS2 = 1, PS1 = 1, PS0 = 0), le contenu du registre TMR0 est incrémenté tous les 128 cycles (ou 128 µs).

Notez que si le contenu du registre TMR0 est 255 (0xFF), il passera à 0 (0x00) à la prochaine incrémentation.

En conclusion, le mode timer est utilisé pour mesurer des durées.

2- Le mode compteur

Pour configurer le module TMR0 en mode compteur, il faut au préalable que :

T0CS = 1 (bit 5 du registre OPTION_REG)

Le contenu du registre TMR0 est alors incrémenté à chaque front du signal présent sur la broche RA4/T0CKI :

• front montant si T0SE = 0 (bit 4 du registre OPTION_REG)

• front descendant si T0SE = 1

En toute rigueur, cela est vrai si le taux de prédivision (prescaler) est réglé à 1 (bit 3 du registre OPTION_REG = PSA = 1).

Avec un taux de prédivision de 32 (PSA = 0, PS2 = 1, PS1 = 0, PS0 = 0), le contenu du registre TMR0 est incrémenté tous les 32 cycles du signal présent sur la broche RA4/T0CKI. En conclusion, le mode compteur est utilisé pour faire du … comptage.

3 – Interruption

On peut activer une interruption quand le registre TMR0 déborde (passage de 0xFF à 0x00).

Registre OPTION_REG

Il s’agit d’un registre spécial situé à l’adresse 0x81 (banque 1) de la mémoire des données (Data RAM).

| Nom | Description | |

| Bit 7 | NOT_RBPU | « Port B Pull-up Enable » • Ce bit doit être mis à 0 pour activer les résistancesde pull-up du port B • Ce bit doit être mis à 1 pour désactiver lesrésistances de pull-up du port B |

| Bit 6 | INTEDG | « Interrupt edge select » • Ce bit doit être mis à 0 pour que l’interruption de labroche RB0/INT soit active sur un front descendant • Ce bit doit être mis à 1 pour que l’interruption de labroche RB0/INT soit active sur un front montant |

| Bit 5 | T0CS | « TMR0 Clock Source Select » • Ce bit doit être mis à 0 pour que l’horloge du module TMR0 soit l’horloge interne (un quart de la fréquence du signal OSC1/CLKIN) • Ce bit doit être mis à 1 pour que l’horloge du module TMR0 soit le signal de la broche RA4/T0CKI |

| Bit 4 | T0SE | « TMR0 Source edge select » Dans le cas où T0CS = 1, le signal d’horloge de la broche RA4/T0CKI est actif : • sur front montant quand T0SE = 0 • sur front descendant quand T0SE = 1 |

| Bit 3 | PSA | « Prescaler assignment » Le prédiviseur est attribué : • au module TMR0 quand PSA = 0 • au Watchdog quand PSA = 1 |

| Bit 2,Bit 1, Bit 0 | PS2, PS1, PS0 | « Prescaler rate select » (Cf. tableau ci-dessous) |

Paramètres du prescaler :

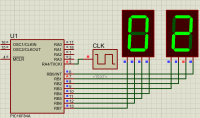

Exemple de configuration de TRISB=0b10000000